# Digital event timer — 1

A versatile and compact c.m.o.s. design

by P.A. Birnie

This timer is intended to replace the expensive mechanical stop watch counterpart by offering a small size of around 100 x 70 x 25mm, about 600 hours of continuous operation from a set of inexpensive mercury cells, and several facilities including two timing channels. Discrete i.cs are used, instead of an I.s.i. device, because they reduce the cost and increase the number of facilities.

When the design of this stopwatch commenced, I expected that an l.s.i. integrated circuit would be used with a few discrete i.cs added to increase the number of facilities. Several designs were constructed using a commercial stopwatch/counter i.c. driven from a

JkHz crystal oscillator, and an l.e.d. \_\_isplay. These were functionally satisfactory but suffered from high power consumption, the need for two different supply voltages, small display size and poor legibility in mild sunlight. The circuit was also difficult to adjust due to the critical monostable elements.

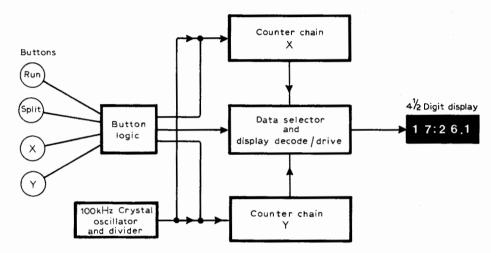

Calculation showed that c.m.o.s. devices, driving a 41/2-digit liquid crystal display from a 5V supply, would require only a few hundred microamps and could give over 600 hours continuous use. The final design allows timing of two events with simultaneous start times, and displays up to 19min 59.9s. After this time the tens of minutes stays at 1 and the units cycle through 0 to 9. A split facility enables the display to be temporarily held while individual events are timed independently from the two channels which continue to count. Cumulative timing of several consecutive events on one channel is also possible and remains independent of the other channel, which can be timing a continuous event. The design can be modified to increase or decrease the number of facilities as required. A block diagram of the circuit is shown in <sup>ા:</sup>વ. 1.

accuracy of the stopwatch is determined by the characteristics of the crystal oscillator components, and in the prototype a 100kHz Statek device was used because of its small size. This

Fig. 1. Block diagram of the stopwatch. Total power consumption for this circuit is between 200 and  $300\mu A$ .

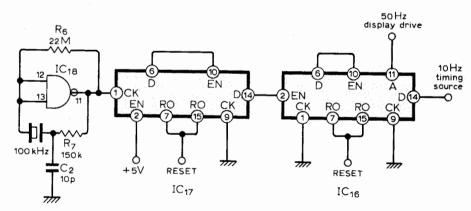

Fig. 2. Crystal oscillator and dividers. A standard Pierce circuit is used with the crystal, C<sub>2</sub>, and input capacitance of the gate acting as the feedback network.

type of crystal is stable and rugged, with an initial setting accuracy of  $\pm 0.02\%$  and a temperature coefficient of +0.0075 to -0.032% from 0 to  $70^{\circ}\text{C}.$  If required a trimmer may be used in the oscillator circuit for more accurate tuning of the resonant frequency. Variations in supply voltage are kept small by using mercury batteries, and the effect of these variations is minimized by selection of the feedback resistor  $R_7$  in the oscillator circuit of Fig. 2. The crystal oscillator output is divided in two dual decade counters to

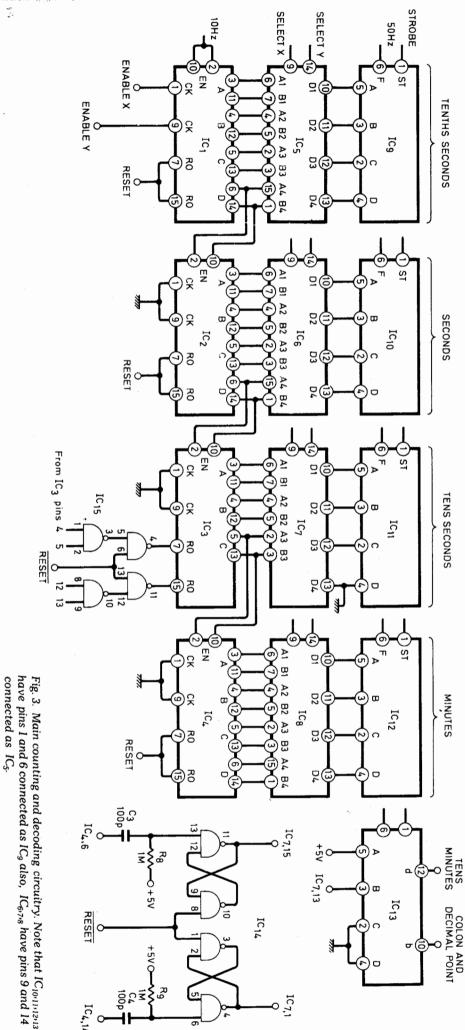

provide a 50Hz drive waveform for the display and a 10Hz timing signal. Four buttons control two 4½-digit counter chains which count up to 19m 59.9s, and a 2:1 data selector is used to route one of these chains to the decoder drivers. The button logic and the main circuit diagram are shown in Figs. 3 and 4.

### Circuit operation

The crystal is used in a standard Pierce oscillator circuit with one gate of  $IC_{18}$  acting as an inverting amplifier. The crystal,  $C_2$  and the input capacitance of

RESET ·O IC<sub>19</sub> 13 RESET IC18 1M +5VC C<sub>1</sub> ENABLE Y • IC<sub>18</sub> R<sub>2</sub> 1M +5VO IC<sub>18</sub> RUN 3 IC19 ENABLE X IC<sub>19</sub> SELECT X IC 19 SELECT Y R<sub>5</sub> STROBE O

| Operation | Timing function                                                                                                                                |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Run       | Resets all logic and starts counters                                                                                                           |  |

| Split     | While depressed, the display is held without interfering with timing functions                                                                 |  |

| <b>x</b>  | Stops channel X and displays content. When the button is released the channel can be restarted by operation of Runwithout affecting channel Y. |  |

| Y         | Stops timing of channel Y. Subsequent depression of Run resets all logic.                                                                      |  |

Fig. 4(a) Button logic, (b) timing function for the buttons.

the gate act as the feedback network. Care has been taken to limit the crystal drive voltage to below 2V pk-pk for reliable operation. A physically larger crystal has been tried in the circuit and, with the addition of a 3-30pF trimmer from the gate input to ground, proved to be entirely satisfactory. The manu-

facturers of the specified crystal do not recommend the use of such a trimmer. A decoupling capacitor, C6, of  $0.01\mu F$  should be placed across the supply and as near to IC<sub>18</sub> as possible to prevent 100kHz appearing across the supply lines to other devices. If an oscilloscope is used to check the oscillator a 10:1 or, better still, 100:1 probe is necessary to prevent significant loading of the circuit.

The oscillator output is applied to the clock input of an up decade counter,  $\frac{1}{2}$  of IC<sub>17</sub>, and the D output is fed to the enable input of the other half of the device. This produces a 1kHz waveform on the second D output which is fed to the enable input of IC16 which also divides by 100. Use of the enable inputs rather than the clock ensures that a negative-going edge is only produced after  $100 \times 100$  input pulses when the two devices have been reset. The second stage of IC<sub>16</sub> produces a 50Hz square wave for driving the display, and a 10Hz waveform for timekeeping purposes.

When the "run" button in Fig. 4 is depressed, the bistable NAND gates are set which makes the enable X and Y lines go low. A negative-going pulse is therefore applied to  $IC_{18}$  via  $C_1$  which produces a high reset pulse for a short period, determined by the time constant  $C_1R_1$ . Because two parts of the circuit require a negative-going reset pulse, a gate of  $IC_{19}$  is used to generate the reset function. The reset pulses act on all of the divider and counter stages in the circuit. When these pulses end, division and counting begins.

Because both clock inputs of  $IC_1$  are low, the first 10Hz falling edge to arrive at the enable inputs of  $IC_1$  causes one increment of the X and Y counters. If no buttons are depressed at this time the select X line will be high and the select Y will be low which causes  $IC_5$  to accept data from the Y counter. This data is passed to  $IC_9$  where it is decoded and used to drive the display. Subsequent negative-going 10Hz clock edges cause further incrementing of the counters in  $IC_1$  until negative-going edges at the two D outputs cause incrementing of

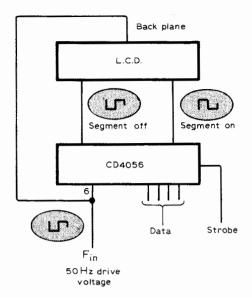

Fig. 5. Generation of the alternating drive voltage. Voltage doubling and cancellation causes the segments to turn on and off respectively.

the X and Y counters in IC2. This process continues until a further button depression displays the contents of the Y counters. The gates in IC15 are used to modify the count sequence so that IC<sub>3</sub> counts from 0 to 5 and then resets. This circuit uses the reset pulse at the start of a timing sequence. Gates IC14 forms two edge-triggered bistable circuits which are set when the D outputs of IC4 produce a negative-going edge. Because IC<sub>3</sub> counts up to 5, IC<sub>7</sub> only has to select a 3-bit word. The spare selector is used to choose the X or Y output from IC14. The last-mentioned circuit therefore stores the state of the 1/2 digit used to indicate tens of minutes.

Depression of the "split" button disables the data inputs of the decoder drivers and the internal data latches in these devices hold the information until the split button is released. The X

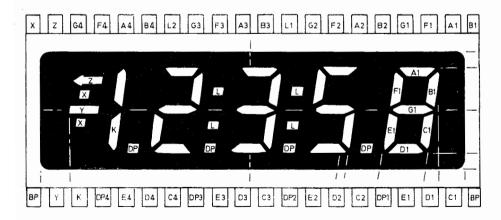

Fig. 6. Liquid crystal display connections

button has two functions. Firstly, IC19 is reset which produces a high on the enable X line to disable the X counter input in IC1. This prevents further incrementing of the X counter chain. Also, while this button is depressed, the select X line is kept low and the Y line high which allows  $IC_{5, 6, 7, 8}$  to display the X counter information. When the button is released the Y counter information is again displayed. The Y button resets IC18 and produces a high on the enable Y line. This disables the Y counter in IC1 and stops further incrementing of the Y counter chain. Note that until the Y button is depressed, the reset pulse is not operated if the run button is used. This feature allows cumulative timing using only the run and X buttons.

### Display

A reflective field-effect display was used in the prototype, which can be powered from 3 to 10V. An alternating drive voltage prevents degradation of the display cell and the circuit arrangement for producing this is shown in Fig. 5. The 50Hz square wave is a compromise between a minimum frequency set by flicker, and a maximum set by increasing display dissipation due to the charge and discharge of display segments. The CD4056 display driver produces antiphase square waves for segments which are to be displayed, and in-phase signals for segments which are turned off. These waveforms are relative to the square wave on the backplane so voltage doubling and cancellation occurs. Display corrections are shown in Fig. 6.

### **Components List**

| 9,10,11,12,13  | CD4019<br>CD4056<br>CD4011            |

|----------------|---------------------------------------|

| 6<br>7<br>8, 9 | 1 ΜΩ<br>22ΜΩ<br>150kΩ<br>1 ΜΩ<br>1 kΩ |

| Capacitors |                    |

|------------|--------------------|

| 1          | 100pF polystyrene  |

| 2          | 10pF silvered mica |

| 3, 4       | 100pF polystyrene  |

| 5          | 47μF 6.3V tantalum |

| 6, 7, 8    | 10µF ceramic       |

**Display** — LXD 7545 (Transworld Scientific, High Wycombe, Bucks)

**Crystal** — SX-1V'A'S, 100kHz (Interface Quartz Devices, Crewkerne, Somerset)

Battery -- 4 × RM675H mercury cells

# Printed circuit boards

Two double-sided p.c.bs will be available for this design. The boards, which are based on the author's layouts to be described next month, are priced at £6.00 for the set and are available from M. R. Sagin at 11 Villiers Road, London N.W.2.

# Digital event timer — 2

# Construction

by P. A. Birnie

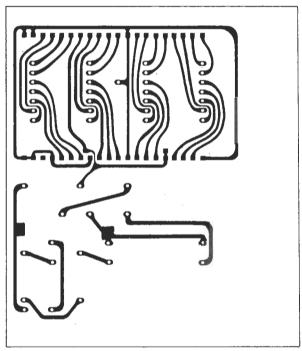

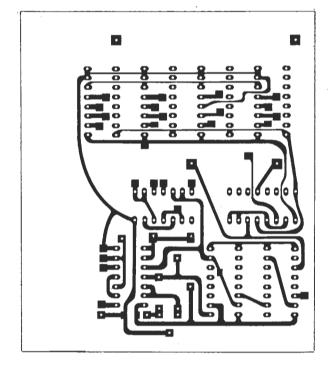

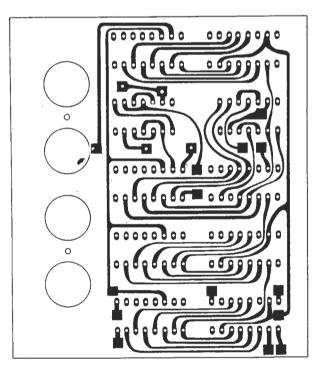

The construction is based on two double-sided printed circuit boards, (see Fig. 7,) which are made from 1mm glass fibre. The layouts can be drawn using an etch resist pen although the accuracy required presents a few difficulties. Both boards should be first drilled using

a 0.8mm bit and a piece of 0.1in Veroboard as a template. The tracks are then drawn in on both sides of the board. Care must be taken to ensure registration between both sides of the board.

The display is mounted on the p.c.b.

Fig. 7. Printed circuit board layout diagram actual size. Note that due to inaccuracies of the printing process and small distortions in the paper, correct registration of the layouts cannot be guaranteed.

## (b) board 2

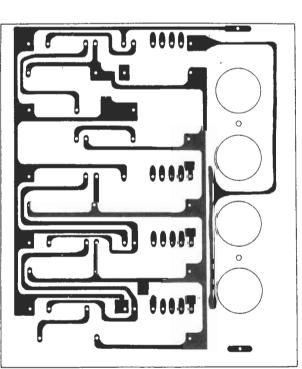

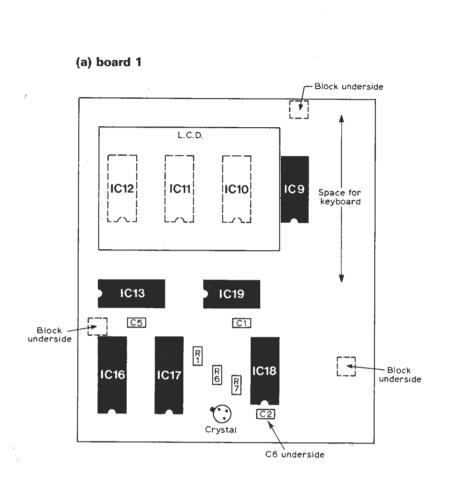

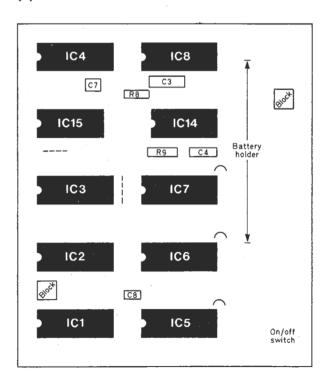

Fig. 8. Component location diagrams. Some of the discrete components are mounted on undrilled pads. Capacitors  $C_{5,6,7,8}$  decouple the supply. Five links are fitted on board (b), three on top and two underneath as shown.

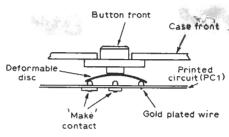

Fig. 9. Button mechanism as used in calculator keyboards.

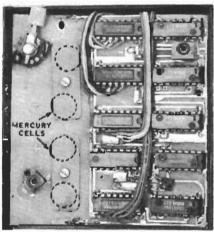

Fig. 10. Component side of p.c.b.2, showing the mounting position of four mercury cells, two blocks for securing the back plate, and the change-over battery switch.

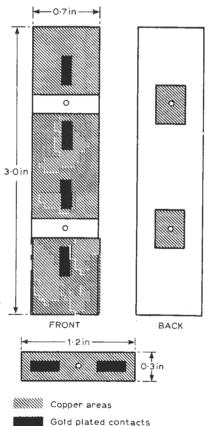

Gold plated contacts All holes 8BA clearance

Fig. 11. Construction details for the ancillary p.c.bs. Boards 4 and 5 are identical and single sided. Board 3 is double sided, the back areas of copper are used to solder the 8BA nuts in place.

using Soldercon i.c.-socket pins. Thirty six of the sockets are mounted and soldered onto the component side of the board and these should be trimmed to remove the unwanted pin. Four socket pins go through the board and are soldered on both sides. All of the pins should be kept in the carrier while they are soldered in place as this makes alignment easier.

The 19 i.cs should be mounted as shown in Fig. 8(a) and (b) using an earthed soldering iron and taking the normal c.m.o.s. precautions. Some of the discrete components do not have holes drilled in the board and these are soldered onto pads on the component side. The TO5 can crystal is mounted upside down with the legs bent over and through 180°. When mounting the display great care should taken because the pins are delicate. Orientation of the display can be determined by examining the readout under strong light. If any of the sockets become detached during insertion, it is safer to continue, and resolder the sockets when the display is in place. Links interconnect pin 9 of IC5, 6, 7, 8 via a track on the component side as shown in Fig. 8(b), pin 11 of  $IC_{15}$  to pin 15 of  $IC_{13}$ , and pin 9 of  $IC_{14}$  to pin 1 of  $IC_7$  via pads on the track side of the board.

Switches in the prototype were constructed from a scrap calculator keyboard, and the mechanism, which is based on a flexible disc of gold-plated metal, is shown in Fig. 9. Construction details of the switches are not given because these components can be adapted to suit the individual.

RM675H mercury cells are mounted on p.c.b.2 as shown in Fig. 10. Three small boards are made using 1mm double sided fibre glass, see Fig. 11, and two of these have the copper removed from one side. Gold battery-contacts are made by carefully removing the goldplated edge connector strips from a scrap board. These strips should be cleaned and soldered in the appropriate positions. It is important to use only a small amount of solder, otherwise contact will be made with the solder rather than the gold. Two 8BA clearance holes are drilled in board 3 and 8BA nuts are soldered to square pads on this board. Using two narrow strips of 1mm Perspex as spacers, board 3 is glued to the non component side of board 2, ensuring that the gold pads align with the 0.5in holes. To make subsequent construction easier, a flying lead is soldered to each end of p.c.b.3 before assembly. The four cells are placed into the cavities which now exist so that the top flying lead is at +5.2Vwith respect to the bottom lead. Boards 4 and 5 are screwed to board 3 using short 8BA screws threading into the nuts already provided.

A change-over switch is needed for the battery because when the power is turned off the decoupling capacitors supply sufficient current to operate the stopwatch for about 8 seconds. After

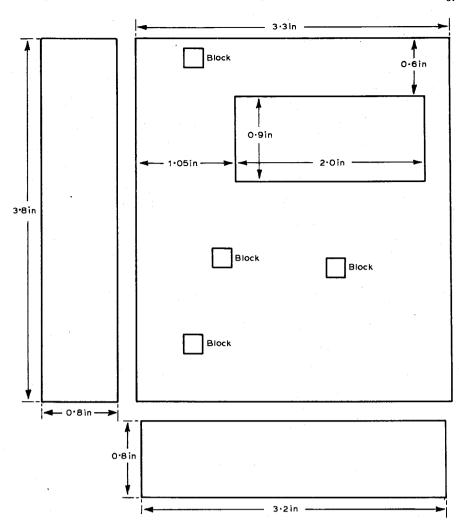

Fig. 12. Case construction details.

Panels are cut from 1mm black

Perspex by scoring and snapping over a

block. The back plate has the same

overall dimensions as the front.

this period the crystal oscillator stops and d.c. is applied to the display for a few seconds. To prevent this potentially damaging situation a  $1k\Omega$  resistor is placed across the supply when the switch is in the off position. The switch is connected to board 2 so that the toggle projects out of the case.

## Case construction

The author's case was made from hein black Perspex and Fig. 12 shows the parts required. The panels should be cut from a Perspex sheet by scoring deeply with a sharp knife and snapping off over a block of wood. This produces a clean edge which should be smoothed off using fine wet and dry paper. Holes for the buttons and display should be cut using the completed p.c.b.1 as a guide. When the case has been glued using a Perspex cement three blocks are built to support board 1. The blocks are glued to the front plate as indicated in Fig. 12, but exact positions require checking to

| Connection on p.c.b.1                                                                                                                                                                                                    | Signal                                                                                   | _                                                                                                                                                                                                                                            | onnection<br>n p.c.b.2                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC <sub>19</sub> - 14<br>IC <sub>18</sub> - 7<br>IC <sub>17</sub> - 7<br>IC <sub>19</sub> - 11<br>IC <sub>19</sub> - 8<br>IC <sub>19</sub> - 10<br>IC <sub>19</sub> - 2<br>IC <sub>18</sub> - 6<br>IC <sub>16</sub> - 14 | +5.2V<br>EARTH<br>RESET<br>RESET<br>SELECT X<br>SELECT Y<br>ENABLE X<br>ENABLE Y<br>10Hz |                                                                                                                                                                                                                                              | IC <sub>1</sub> , 16<br>IC <sub>5</sub> , 8<br>IC <sub>1</sub> , 15<br>IC <sub>1</sub> , 13<br>IC <sub>5</sub> , 9<br>IC <sub>5</sub> , 14<br>IC <sub>1</sub> , 1<br>IC <sub>1</sub> , 9<br>IC <sub>1</sub> , 2 |

| IC9, 5<br>IC9, 3<br>IC9, 2<br>IC10, 5<br>IC10, 3<br>IC10, 3<br>IC10, 2<br>IC10, 4<br>IC11, 5<br>IC11, 3<br>IC11, 2<br>IC12, 5<br>IC12, 3<br>IC12, 2<br>IC12, 4<br>IC13, 3                                                | TENTHS SECONDS  UNITS SECONDS  TENS SECONDS  UNITS MINUTES  TENS MINUTES                 | 20<br>21<br>22<br>23<br>20<br>21<br>22<br>23<br>20<br>21<br>22<br>20<br>21<br>22<br>20<br>21<br>22<br>20<br>21<br>20<br>21<br>20<br>21<br>20<br>21<br>20<br>21<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 | IC5- 10 IC5- 11 IC5- 12 IC5- 13 IC6- 10 IC6- 11 IC6- 12 IC6- 13 IC7- 10 IC7- 11 IC7- 12 IC8- 13 IC7- 12 IC8- 13 IC7- 12 IC8- 13 IC7- 12 IC8- 13 IC7- 12                                                         |

| IC <sub>18</sub> , <sub>5</sub> IC <sub>10</sub> , <sub>1</sub> IC <sub>19</sub> , <sub>8</sub> IC <sub>18</sub> , <sub>1</sub>                                                                                          |                                                                                          | · c                                                                                                                                                                                                                                          |                                                                                                                                                                                                                 |

ensure that no projections exist on the non-component side of board 1. Holes are carefully drilled through this board and into the blocks to accommodate self tapping screws. A similar approach is adopted for board 2 except that the blocks are glued, using Araldite, to board I as shown in Fig. 8. Care should be taken not to cut or bridge any pads while drilling the p.c.bs. The back of the case is also secured to board 2 by Perspex blocks. If the block positions shown in Fig. 8 are not used, board I should be supported around the pushbutton switches to prevent excessive flexing during use. The case can be polished using metal polish or T-cut.

## Final assembly and testing

The two main component boards are interconnected by two groups of miniature flat ribbon cable as listed in the table. Pads are provided on both sides of the boards for these wires. The first group contains 16 wires interconnecting the outputs of the data selector stages to the display decoder drivers. The second group of wires provides clock and control signals from board 1 to board 2. Connections from the four push-buttons to board I are also shown. Final connections are by flying leads from the battery holder to the positive supply rail on board 2, and the negative supply rail, via a multimeter, to the switch. After a final check, and with the multimeter on the 10mA range, switch on. An initial large deflection should take place as all the decoupling capacitors charge. The current should then drop to about 200µA and the display should be active. If this is the case, the button functions can be tested. When all of the operations have been success-

Fig. 13. Internal view of the timer with p.c.b.2 hinged open. Board 2 is supported on board 1 by three Perspex blocks

fully tested the two boards should be inserted into the case and secured in position. It should be noted that the display segments have a relatively long response time. This is normal especially in warm ambient temperatures. It is possible to use other liquid crystal displays in this design provided that they use the same drive of five volts r.m.s.

#### Printed circuit boards

Two double-sided p.c.bs will be available for this design. The boards, which are based on the author's layouts, are priced at £6.00 for the set and are available from M. R. Sagin at 11 Villiers Road, London N.W.2.